International Journal of Scientific Engineering and Technology Research

ISSN 2319-8885 Vol.03,Issue.06, May-2014, Pages:0912-0919

www.semargroup.org, www.ijsetr.com

# **Design and Implementation of Digital Trainer Board for Laboratory** Myo Su Su THEINT<sup>1</sup>, ZAW Myo TuN<sup>2</sup>

<sup>1</sup>Electronic Department, Mandalay Technological University, Mandalay, Myanmar, Email: myonyein87@gmail.com. <sup>2</sup>Electronic Department, Mandalay Technological University, Mandalay, Myanmar, Email: zawmyotun.mtu@gmail.com.

**Abstract:** This paper deals with the design, development, and implementation of digital trainer board for laboratory. The main aim of the proposed system is to design and implement a , cost effective and reliable digital trainer board for laboratory. The system contains five sections, power supply unit, function generator unit, digital unit, breadboard and decoder/encoder. The power supply unit includes regulated 5V,  $\pm 12V$  and  $\pm 20V$ . The function generator unit is to be designed with XR-2206 IC. This IC is capable of producing high quality sine, square and triangle waveform of stability and accuracy. The basic digital ICs such as AND, NAND, OR, NOR, and NOT are used to apply for the combinational logic design.

Keywords: Digital trainer, Power supply, Logic gate, Function generator, Decoder/encoder.

# I. INTRODUCTION

Rapid changes in the field of engineering technology have increased the need for universities to provide engineering and engineering technological students with meaningful and relevant practical experiences. To partial fulfill this need, study on implementation of digital trainer board has been done. The research includes the development, design and implementation of digital trainer board for students. The designed digital trainer contains 5 sections; the power supply section, the function generator section, the digital logic section and the test bench (breadboard).The power supply section can produce regulated 5 volts DC output, regulated  $\pm$  12 volts, and  $\pm$ 20 volts DC supply for the tested circuit using digital trainer. The function generator section can produce the sine wave, square wave and triangle wave with the frequency range from 1 Hz to 100 kHz.

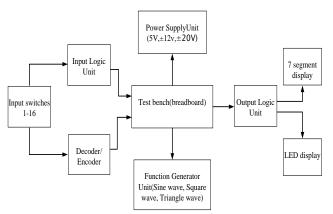

Fig.1.Block Diagram of the System

The digital logic section contains, AND gate, NAND gate, OR gate, NOR gate and NOT gate with control

switches and LEDs. The output of the function generator can be tested with oscilloscope. Sixteen switches labeled SW1 to SW16 are applied as an input in this system. When the desirable switches and input logic gates are connected by using conductor, the output results are shown in LED. The output of the encoder/decoder is displayed in the seven segment display or LEDs. The block diagram of the system is shown in figure 1.

#### **II. HARDWARE IMPLEMENTATION**

Hardware implementation is consisted of power supply unit, logic gate unit, function generator section and encoder/ decoder section.

## A. Power Supply Unit

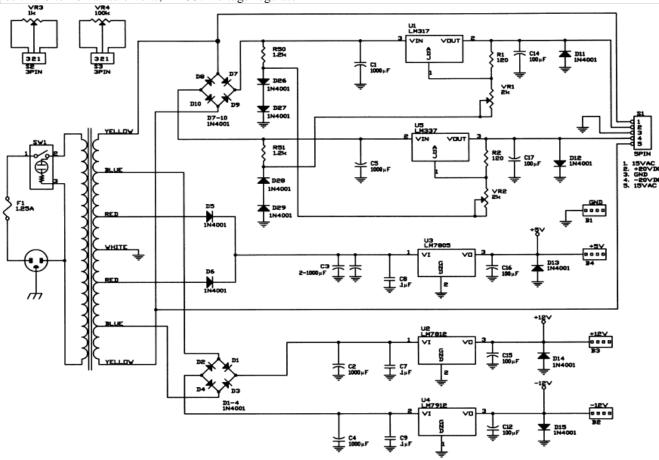

Initial state of electronic circuit is power supply system which provides required power to drive the whole system. The specification of power supply depends on the power requirement and this requirement is determined by its rating. The main components used in supply system are transformer, rectifier, input filter, regulator and output filter. The power supply section includes two variable, supplies giving up to  $\pm$  20 volts at 0.5 ampere. Below 15 volts, the current available is over 1 ampere. Three fixed power supplies give the user +12 V DC, - 12 V DC or +5 V DC at 1 ampere each. These fixed voltages are the most commonly used voltages for design work. All supplies are regulated to within 150 mV. The user can increase current draw from no load to 0.5 amperes and the voltage will change less than 150 mV. All supplies are short circuit protected by using integrated circuit regulator devices.

To obtain 5-volt power supply, full wave center-tapped rectifier, LM7805 voltage regulator, and capacitors are used.

Full wave center-tapped rectifier includes stepped down transformer (220 V AC to 18V AC and 12 V AC), two (1N4007) diodes are used to rectify AC voltage and the capacitors are used to reduced ripples and regulate the voltage. To obtain positive and negative 12-volt power supply full wave bridge rectifier, LM7812 voltage regulator for positive 12 volts regulation, LM7912 voltage regulator for negative voltage regulation and capacitors are used. Full wave bridge rectifier includes stepped down transformer (220 V AC to 18V AC and 12 V AC), four (1N4007) diodes are used to rectify AC voltage and the capacitors are used to reduced ripples and regulate the voltage. When the circuit for negative power supply is being implemented, it has to make sure that the positive end of capacitor must be grounded. Otherwise, the capacitor will be burst out.

To obtain positive and negative 20-volt variable power supply full wave bridge rectifier, LM317 voltage regulator for positive 0 to 20 variable volts, LM337 voltage regulator

for negative variable voltages, resistor and capacitors are used. Full wave bridge rectifier includes stepped down transformer (220 V AC to 24V AC), four (1N4007) diodes are used to rectify AC voltage and the capacitors are used to reduced ripples and regulate the voltage.. When the circuit for negative power supply is being implemented, it has to make sure that the positive end of capacitor must be grounded. Otherwise, the capacitor will be burst out. Moreover, input, output and ground pins of the regulator ICs are also taken in care. The regulator ICs, LM317 and LM337 are operated as floating regulators because the adjustment terminals are not connected to the ground but float to whatever the voltages across 2 k $\Omega$  resistors. This allows the output voltages to be much higher than that of a fixed voltage regulator. After implementing each power supply, the final power supply circuit is assembled together. The overall power supply circuit diagram is shown in figure 2.

#### Fig.2.Overall Power Supply Circuit

#### **B.** Logic Gate Section

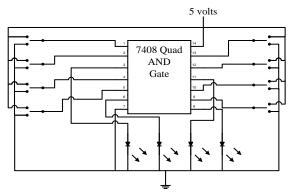

The logic gate section contains AND gate subsection, NAND gate subsection, OR gate subsection, NOR gate subsection and NOT gate subsection. AND gate subsection has been implemented with 74HC08 AND gate IC. This IC contains four AND gates. First of all, the AND gate test circuit is constructed. This circuit is very simple and shown in figure 4.5. Eight switches are used to give inputs for four AND gates and four LEDs are used to check the outputs.

Fig.3. AND Gate Test Circuit

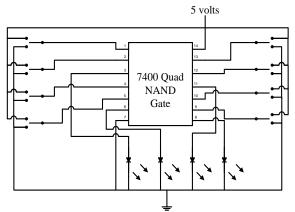

NAND gate subsection has been implemented with 74HC00 NAND gate IC. This IC contains four NAND gates. NAND gate test circuit is constructed as shown in figure 4. Eight switches are used to give inputs for four NAND gates and four LEDs are used to check the outputs.

Fig.4.NAND Gate Test Circuit

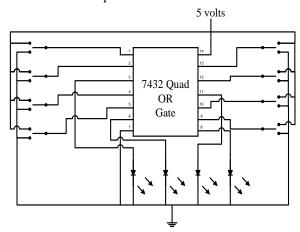

OR gate subsection has been implemented with 74HC32 OR gate IC. This IC contains four OR gates. OR gate test circuit is constructed as shown in figure 5. Eight switches are used to give inputs for four OR gates and four LEDs are used to check the outputs.

Fig.5. OR Gate Test Circuit

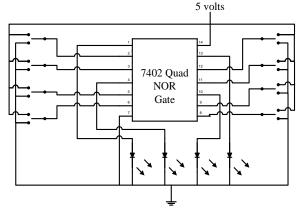

NOR gate subsection has been implemented with 74HC02 NOR gate IC. This IC contains four NOR gates. NOR gate test circuit is constructed as shown in figure 6. Eight switches are used to give inputs for four NOR gates and four LEDs are used to check the outputs.

Fig. 6. NOR Gate Circuit Test

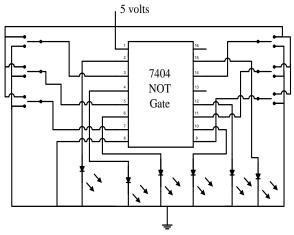

NOT gate subsection has been implemented with 74HC02 NOT gate IC. This IC contains six NOT gates. NOT gate test circuit is constructed as shown in figure 7. Six switches are used to give inputs for six NOR gates and six LEDs are used to check the outputs.

Fig.7.NOT Gate Circuit Test

#### **C. Function Generator Section**

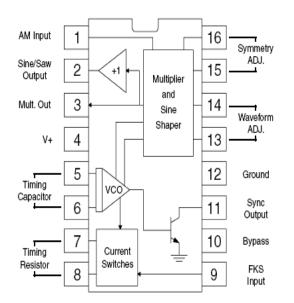

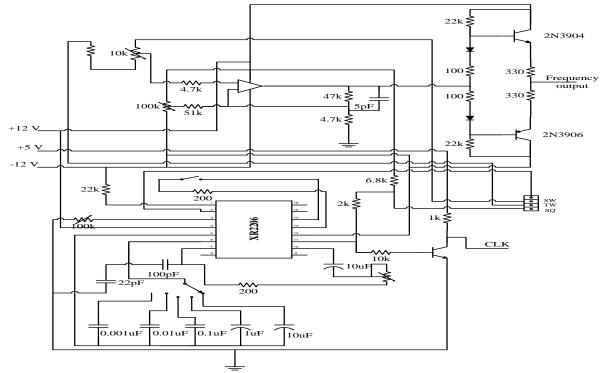

The trainer contains a complete function generator capable of producing sine, square and triangle waveform. The frequency of this generator is continuously variable from one hertz to over 100,000 hertz in five steps. A fine tuning control makes selection of any frequency easy. The output voltage amplitude is variable between 0 to 15Vpp. The output impedance is approximately 330 ohms. The function generator frequencies are produced by an XR-2206 integrated circuit. This IC is capable of producing high quality sine, square, and triangle waveform of high stability and accuracy. Figure 8 shows the block diagram of the XR-2206 IC.

International Journal of Scientific Engineering and Technology Research Volume.03, IssueNo.06, May-2014, Pages: 0912-0919

Fig8. Internal Diagram of XR-2206 Function Generator IC.

The XR-2206 is comprised of four main functional blocks. They are voltage controlled oscillator (VCO), analog multiplier and sine-shaper, unity gain buffer amplifier and a set of current switches. The VCO actually produces an output frequency proportional to an input current, which is produced by a resistor from the timing terminals to ground. The current switches route one of the currents to the VCO to produce an output frequency. Which timing pin current is used, is controlled by the FSK input (pin 9). In this trainer, the FSK input is left open, thus only the resistor on pin 7 is used. The frequency is determined by this formula:

$$f_0 = 1/RC Hz$$

(1)

Where,  $f_o$  is the frequency in Hertz, R is the resistance at pin 7 in Ohms and C is the capacitance across pin 5 and 6 in Farads.

The resistance between pins 13 and 14 determines the shape of the output wave on pin 2. No resistor produces a triangle wave. A 200 $\Omega$  resistor produces a sine wave. Figure 9 shows the circuit schematic diagram of function generator.

Fig.9. Circuit Schematic Diagram of Function Generator

## **D. Encoder / Decoder Section**

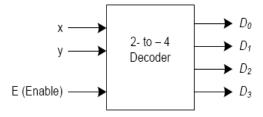

The last section of digital trainer board is the Encoder / Decoder Section. A decoder is a combinational circuit that converts coded inputs to other coded outputs. The famous examples of decoders are binary n-to- $2^n$  decoders and seven-segment decoders. A binary decoder has n inputs and a maximum of  $2^n$  outputs. Figure 10 shows the 2 to 4 Decoder and the truth table of this decoder is shown in Table 1.

Fig. 10. 2 to 4 Decoder

International Journal of Scientific Engineering and Technology Research Volume.03, IssueNo.06, May-2014, Pages: 0912-0919

| Table 1. The Truth Table | of 2 t | o 4 Decoder |

|--------------------------|--------|-------------|

|--------------------------|--------|-------------|

| Е | x                | У |   | $D_1$ | $D_2$ | D3 |

|---|------------------|---|---|-------|-------|----|

| 0 | X<br>0<br>0<br>1 | Х | 0 | 0     | 0     | 0  |

| 1 | 0                | 0 | 1 | 0     | 0     | 0  |

| 1 | 0                | 1 | 0 | 1     | 0     | 0  |

| 1 | 1                | 0 | 0 | 0     | 1     | 0  |

| 1 | 1                | 1 | 0 | 0     | 0     | 1  |

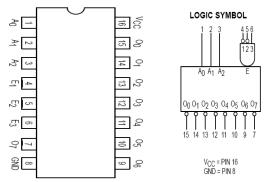

In this research work, 74LS 138 is used as a decoder. It is a 3 to 8 line decoder and its pin diagram is shown in Figure 11.

Fig. 11.Pin Diagram of 74LS138

Table 2. Truth Table of 74LS138 decoder IC

|   | INPUTS |    |    |                |    |    |    |    | 0U | TPUTS |    |    |    |

|---|--------|----|----|----------------|----|----|----|----|----|-------|----|----|----|

| Ē | E2     | E3 | Ao | A <sub>1</sub> | A2 | 00 | 01 | 02 | 03 | 04    | 05 | 06 | 07 |

| Н | Х      | Х  | χ  | Х              | Х  | Н  | Η  | Н  | Н  | Н     | Н  | Н  | Н  |

| Х | Н      | Х  | Х  | Х              | Х  | Н  | Н  | Н  | Н  | Н     | Н  | Н  | Н  |

| Х | Х      | L  | Х  | Х              | Х  | Н  | Н  | Н  | Н  | Н     | Н  | Н  | Н  |

| L | L      | Η  | L  | L              | L  | L  | Н  | Н  | Н  | Η     | Н  | Η  | Н  |

| L | L      | Η  | H  | L              | L  | Н  | L  | Н  | Н  | Η     | Н  | Η  | Н  |

| L | L      | Η  | L  | Н              | L  | Н  | Н  | L  | Н  | Н     | Н  | Η  | Н  |

| L | L      | Η  | Н  | Н              | L  | Н  | Η  | Н  | L  | Η     | Н  | Η  | Н  |

| L | L      | Η  | L  | L              | Η  | Н  | Н  | Н  | Н  | L     | Н  | Η  | Н  |

| L | L      | Η  | Н  | L              | Η  | Н  | Н  | Н  | Н  | Η     | L  | Η  | Н  |

| L | L      | Н  | L  | Н              | Н  | Н  | Н  | Н  | Н  | Н     | Н  | L  | Н  |

| L | L      | Η  | H  | Η              | Η  | Η  | Η  | Η  | Η  | Η     | Η  | Η  | L  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

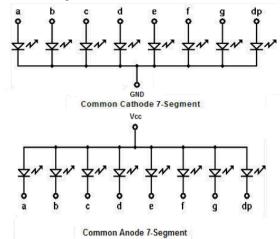

Another common type of decoder is the seven-segment decoder. This decoder is used along with seven-segment LED display to create decimal or hexadecimal digits. The Seven-segment LED display is commonly used for numerical display as in multimeters and calculators, it contains seven independent LEDs arranged as shown in Figure 12.

Fig.12. 7 Segment Display

There are two main types of seven-segment LEDs, the common cathode (CC) and the common anode (CA). In the CC type, the cathodes for all segments are joined in a single node. On the other hand in CA type, the anodes are joined together in a single node.

Figure 13. Common Cathode and Common Anode 7 segment Internal Diagram.

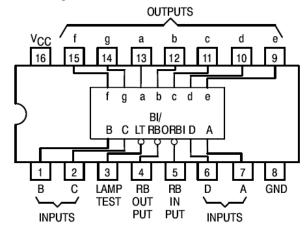

All decimal or hexadecimal numbers can be displayed by controlling the state of the appropriate segments ON or OFF. This can be done using a seven-segment decoder, a seven-segment decoder accepts four binary inputs and provides seven outputs that determine which of the segments on a seven-segment LED display should be on or off to create a decimal or hexadecimal digits. As an example of the commercial 7-segment decoder is the 74LS248 chip, this is a BCD to seven-segment decoder which used for displaying the numbers from 0 through 9 based on the corresponding input BCD number. This chip is design for use with to a common anode seven segment display.

In this research, 74LS248 BCD to Decimal decoder is used with 7 segment display. Pin Diagram of this IC is shown in Figure 14.

Fig. 14. Pin Diagram of 74LS248IC.

International Journal of Scientific Engineering and Technology Research Volume.03, IssueNo.06, May-2014, Pages: 0912-0919

The truth table of the decoder circuit with 7 segment display is shown in table 3.

| DECIMAL<br>OR        |             |                  | INP         | UTS         |                  |                  |             | BURBOT           |                  |                  |             |                  |             |             | NOTE        |  |  |

|----------------------|-------------|------------------|-------------|-------------|------------------|------------------|-------------|------------------|------------------|------------------|-------------|------------------|-------------|-------------|-------------|--|--|

| FUNCTION             | LT          | RBI              | D           | С           | В                | A                | DI/RDU      | a                | b                | с                | d           | e                | f           | g           | NUL         |  |  |

| 0<br>1<br>2<br>3     | H H H H     | H<br>X<br>X<br>X |             | L<br>L<br>L | L<br>L<br>H<br>H | L<br>H<br>L<br>H | H<br>H<br>H | H<br>L<br>H<br>H | H<br>H<br>H      | H<br>H<br>L<br>H | H L H H     | H<br>L<br>H<br>L | H L L L     | LLHH        | 1<br>1      |  |  |

| 4<br>5<br>6<br>7     | H H H H     | X<br>X<br>X<br>X |             | H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | ннн         | L<br>H<br>H      | H<br>L<br>H      | H<br>H<br>H      |             | L<br>L<br>H<br>L | H<br>H<br>L | H H H L     | 1           |  |  |

| 8<br>9<br>10<br>11   | H H H H     | X<br>X<br>X<br>X | H<br>H<br>H | L<br>L<br>L | L<br>L<br>H<br>H | L<br>H<br>L<br>H | H H H H     | H<br>H<br>L<br>L | H<br>H<br>L<br>L | H<br>H<br>L<br>H | H H H H     | H L H L          | H H L L     | нннн        |             |  |  |

| 12<br>13<br>14<br>15 | H H H H     | X<br>X<br>X<br>X | H H H H     | H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | нннн        | L<br>H<br>L<br>L | H<br>L<br>L      |                  | ーエエー        | LLHL             | ΗΗΗL        | I I I I     |             |  |  |

| BI<br>RBI<br>LT      | X<br>H<br>L | X<br>L<br>X      | X<br>L<br>X | X<br>L<br>X | X<br>L<br>X      | X<br>L<br>X      | L<br>L<br>H | L<br>L<br>H      | L<br>L<br>H      | L<br>L<br>H      | L<br>L<br>H | L<br>L<br>H      | L<br>L<br>H | L<br>L<br>H | 2<br>3<br>4 |  |  |

Table3. Truth Table for BCD to 7 Segment Display

## **III. RESULTS**

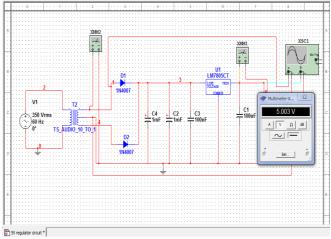

The simulation of power supply section has been done in Multisim. The circuits for regulated power supplies  $\pm 12$  V, + 5V and variable power supply  $\pm 20$  V are simulated separately. Figure 15 shows the simulation window for positive 5 volts power supply circuit. The simulation result is satisfactory.

Figure 15: Simulation Window for Positive 5 Volts Power Supply Circuit.

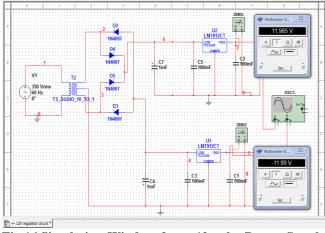

Figure 16 shows the simulation results for positive and negative 12 volts dual power supply circuit. The results are also satisfactory.

Fig.16.Simulation Window for ± 12 volts Power Supply Circuit.

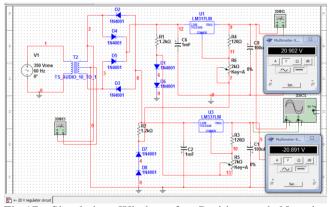

Figure 17 shows the simulation results for  $\pm$  20 volts variable power supply circuit. The variable voltages are ranged from nearly 0 volt to positive and negative 20 volts. The variable voltages are controlled with the variable resistors  $R_5$  and  $R_6$  in the circuit by varying the resistor values. The voltages increase as resistance values in R5 and R6 increases and vice versa. As shown in figures simulation results are satisfactory.

Fig.17. Simulation Window for Positive and Negative Output Voltages of  $\pm$  20 V Power Supply Circuit.

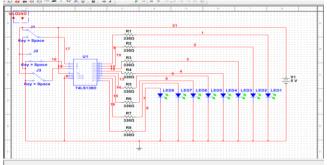

Figure 18 shows the simulation result for encoder circuit where 74LS138IC is used.

Fig. 18. Simulation Window for encoder

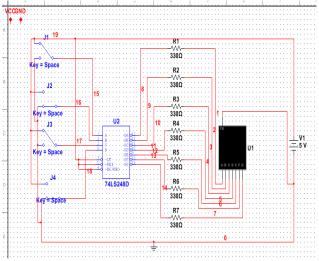

International Journal of Scientific Engineering and Technology Research Volume.03, IssueNo.06, May-2014, Pages: 0912-0919 Figure 19 shows the simulation result for decoder circuit where 74LS248 IC is used.

Fig.19. Simulation Window for decoder.

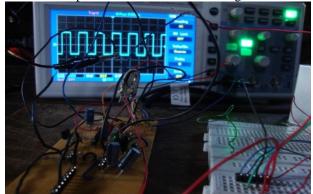

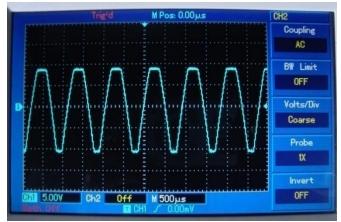

Figure 20 shows the output result for square wave testing with oscilloscope. The result is satisfied and good.

Fig.20.The output result of square wave

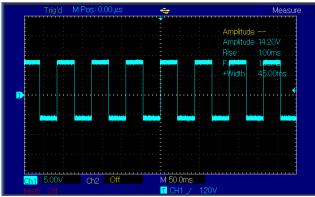

Figure 21 shows the output result for square wave where  $10\mu F$  capacitor and  $2k\Omega$  resistor is used. The output frequency is 10Hz and the output voltage Vpp is 14.20V.

Fig.21. The Output Square Waveform

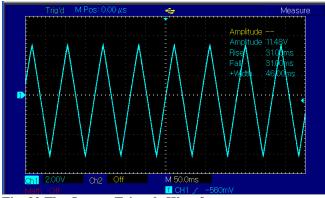

Figure 22 shows the output result for triangle wave where  $10\mu F$  capacitor and  $2k\Omega$  resistor is used. The output frequency is 10Hz and the output voltage Vpp is 11.48 V.

Fig. 22. The Output Triangle Waveform

Figure 23 shows the output result for sine wave where  $0.1\mu F$  capacitor and  $2k\Omega$  resistor is used. The output frequency is 1Hz and the output voltage Vpp is 12 V.

Fig. 23. The Output Sine Waveform.

| Table3.Relation between in | put and output values |

|----------------------------|-----------------------|

|----------------------------|-----------------------|

| Input<br>value |           | Sine w    | vave                   | Square    | e wave                 | Triangle<br>wave |                        |  |

|----------------|-----------|-----------|------------------------|-----------|------------------------|------------------|------------------------|--|

| R(<br>Ω)       | C(µF<br>) | F(H<br>z) | V <sub>pp</sub><br>(V) | F(Hz<br>) | V <sub>pp</sub><br>(V) | F(Hz<br>)        | V <sub>pp</sub><br>(V) |  |

| 2k             | 10        | 10        | 12.1                   | 10        | 14.2                   | 10               | 11.48                  |  |

| 2k             | 1         | 100       | 11.48                  | 100       | 14.2                   | 100              | 11.48                  |  |

| 2k             | 0.1       | 1k        | 11.49                  | 1k        | 14.2                   | 1k               | 11.05                  |  |

| 2k             | 0.01      | 10k       | 10.98                  | 10k       | 14.1                   | 10k              | 10.97                  |  |

| 2k             | 0.00<br>1 | 100<br>k  | 11.02                  | 100k      | 14.4<br>5              | 100k             | 10.22                  |  |

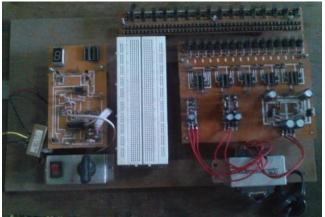

After design and construction of the whole circuit, test and result is carried out. Figure 24 shows complete constructed circuit of digital trainer board for laboratory.

International Journal of Scientific Engineering and Technology Research Volume.03, IssueNo.06, May-2014, Pages: 0912-0919

Fig.24. Circuit Overview of the System

## **IV. SUMMARY**

The hardware design and software implementation of the digital trainer board is described. The simulation results of power supply section and decoder/encoder section have been done in Multisim. Sixteen switches labeled SW1 to SW16 are applied as an input in this system. The output results are tested with oscilloscope. The function generator section can produce the sine wave, square wave and triangle wave with the frequency range from 1 Hz to 100 kHz.

# **V. CONCLUSION**

The digital trainer board for laboratory is described. The components required in trainer board are chosen. The overall circuit for trainer board is designed. The output results for function generator are described in table.3. The proposed system can be implemented to perform higher standard than any other commercial products. An inexpensive and excellent digital trainer board is designed and implemented. Multisim software is used for simulation. This result is convenient and simple for students to test.

# **VI. REFERENCES**

[1] Inderpreet Kaur (Asstt.Prof), Rayat and Bahra Institute of Engineering and Bio-technology, Mohai, India, Microcontroller Based Home Automation System with Security".

[2] Umm Al-Qura University, Computer Engineering Department, "Digital Design Lab Manual".

[3] http://www.elenco.com/digital/analog trainer/XK 550.

[4] EcE-2022 Digital Electronics, Department of Electronic Engineering Department of Technological and Vocational Education, Ministry of Science and Technology, Myanmar.

[5] www.ALLDATASHEET.com

[6] 1972 EXAR Corporation, Datasheet June 1997.